이번 게시물은 반도체에서 가장 기본적인 내용인 낸드 플래시 메모리에 대해 알아보자.

1. 정의

플래시 메모리의 한 형태로 전원이 없는 상태에서도 데이터를 계속 저장할 수 있으며 데이터를 자유롭게 저장·삭제할 수 있다. 저장단위인 셀을 수직으로 배열해 좁은 면적에 많은 셀을 만들 수 있도록 돼 있어 대용량이 가능하다.

전원이 꺼지더라도 저장된 데이터를 보존하는 롬(ROM)의 장점과 정보의 입출력이 자유로운 램(RAM)의 장점을 동시에 지닌 특성 때문에 디지털 카메라, MP3, 휴대전화, USB 드라이브 등 휴대형 기기에서 대용량 정보 저장 용도로 사용된다.

※ nand flash vs nor flash

플래시 메모리는 반도체 칩 내부의 전자회로 형태에 따라 NAND(데이터 저장)형과 NOR(코드 저장)형으로 구분된다. 낸드플래시는 용량을 늘리기에 쉽고, 노어 플래시는 읽기 속도가 빠른 장점을 가지고 있다.

※ D램과 비교

- 정보를 저장한다는 점은 D램과 같지만 전원이 꺼져도 저장한 정보가 사라지지 않는다는 장점을 지니고 있다.

- 일반적으로 D램은 트랜지스터 1개와 커패시터 1개로 셀이 구성되지만, 플래시 메모리는 트랜지스터 1개로 하나의 셀을 구성한다. 플래시 메모리는 전기적인 방법으로 정보를 자유롭게 입출력할 수 있으며, 전력소모가 적고 고속프로그래밍이 가능하다.

2. 구조 및 원리

- 기본적인 MOSFET 구조에 플로팅 게이트(부유 게이트)가 추가된 형태

- 플로팅 게이트에 전자를 저장함으로써 데이터를 저장

- 플로팅 게이트에 전자가 있으면(많으면) 0 으로 인식 (programmed)

- 플로팅 게이트에 전자가 없으면(적으면) 1 로 인식 (erased, unprogrammed)

기본 구조는 이렇지만, 현재는 플로팅게이트가 아닌 산화막에 전자를 저장해버리고 플로팅게이트를 생략해버리는 식(삼성, CTF) 등의 발전된 방식이 많이 존재

그럼 저 플로팅 게이트에 어떻게 전자를 넣을까요. 컨트롤 게이트에 강력한 (+)전압을 걸어주면 됩니다. 그러면 바디(P-well 이라고 쓰여진 영역)의 전자가 위쪽으로 모입니다. 음극인 전자가 양극인 게이트쪽으로 인력을 받음.

그런데 중간에 절연층(산화막)이 버티고 있습니다. 산화막은 기본적으로 전자가 통과할 수 없습니다. 하지만 플래시메모리에서는 전자가 통과해야 데이터를 저장하든 말든 하겠지요. 그래서 12~24V의 고전압을 걸어버립니다.

드레인 측에도 그 정도는 아니지만 높은 전압을 걸어줍니다. 이 정도의 강력한 전계가 형성되면 전자가 충분한 에너지를 얻어서 산화막을 통과해버립니다.(Hot electron effect)

통과한 전자는 플로팅게이트에 저장되어 전계가 사라져도 산화막에 의해 외부로 유출되지 않습니다. 전원이 끊어져도 데이터가 사라지지 않는거지요.

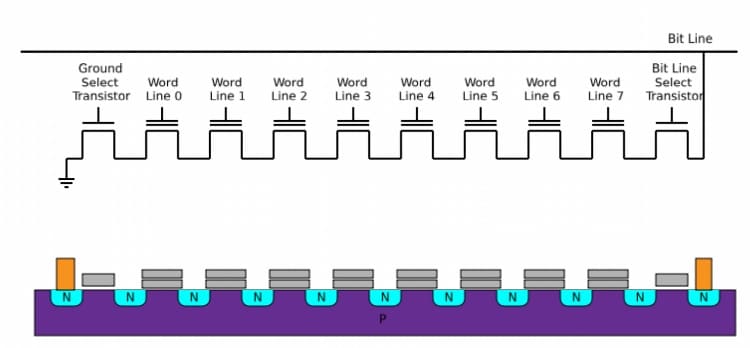

아래는 낸드플래시 셀의 구조입니다. 하나의 비트라인(Bit Line)에 다수의 셀이 직렬로 연결되어 있습니다. 비트라인에 전압을 걸면 직렬로 연결된 모든 셀에 전압이 걸리고, 워드라인(Word Line), 즉 컨트롤 게이트에 전압을 걸린 셀에만 채널이 형성됩니다. 읽기 과정은 이 채널의 존재유무에 달려있습니다.

전자가 있는(Program) 된 셀의 문턱전압은 0V보다 크고, 전자가 없는(Erase) 된 셀의 문턱전압은 0V보다 작습니다.

비트라인에 전압을 걸고, 읽으려는 셀의 워드라인에는 0V, 그 외 셀의 워드라인에는 6~6.5V 정도를 인가합니다.

6~6.5V는 셀의 상태와 관계없이 채널을 형성할 수 있는 문턱전압입니다.

> 플로팅게이트에 전자가 저장된 경우.

읽으려는 셀에 전자가 있는 경우 워드라인에 0V를 인가해도 채널이 형성되지 않습니다. 나머지 셀에는 채널이 형성되었으니 선택된 셀에서 open되어 버린 것으로 볼 수 있습니다. 이러니 비트라인에 전압이 걸려도 전류가 잘 흐르지 않습니다.

open 상태이기때문에 비트라인을 통해 유입되는 전류는 빠져나가지 못 하고 charge가 됩니다. 비트라인의 전압강하가 적게 되고 이를 '0'으로 인식합니다.

> 플로팅게이트에 전자가 없는 경우

읽으려는 셀에 전자가 없으면 0V를 인가해도 채널이 잘 형성되고 전류가 잘 흐릅니다. Short 상태이니 비트라인을 통해 유입되는 전류가 charge되지 못 하고 비트라인의 전압강하는 커집니다. 이를 '1'로 인식합니다.

플래시메모리에 데이터를 저장하기 위해서는 플로팅게이트를 비울 필요가 있습니다. 저장될 데이터가 0(전자저장필요)인지 1(전자저장불필요)인지 알 수 없는 상황에서 플로팅게이트에 전자가 남아있으면 제대로 데이터를 기록할 수 없습니다. 플로팅게이트를 완전히 비워야합니다. 방법은 쓰기의 반대입니다.

바디(P형)쪽에 12~24V의 강력한 전압을 걸어 쓰기때와 반대반향의 전계를 형성, 플로팅게이트 내의 전자를 바디(P형)쪽으로 끌어냅니다. 소스 측에도 (+)전압을 걸어 쓰기 때와 반대 현상이 일어나도록 유도합니다.

SSD의 경우 이렇게 각 셀의 데이터를 지우는 작업을 쓰기작업이 발생하기 전에 미리 진행해놓는데 이를 Trim이라고 합니다. 쓰기 속도 향상에 필수적인 과정입니다.

CTF [ Charge Trap Flash ]

타노스라는 신물질을 이용해 전하를 도체가 아닌 부도체에 저장시켜 플로팅게이트를 없애는 기술. 그만큼 소자 부피가 줄고 인접한 셀 간에 간섭을 최소화하기 때문에 50나노(10억분의 1미터) 이하 초미세 공정의 기술로 평가된다.

3차원 V낸드 [ 3D vertical NAND ] - 3차원 수직구조 낸드(NAND)

평면(2차원) 위에 많은 회로를 넣는 대신 3차원 수직구조로 회로를 쌓아올려 집적도를 높인 플래시메모리 기술이다. 휴대전화, 디지털카메라 등의 기기에서 데이터를 저장하는 장치로 쓰인다. 기존 2차원 평면구조의 메모리 공정이 10나노급에 달해 셀 간 간격이 좁아져 전자가 누설되는 현상이 심화되는 등 한계를 보이자 이를 극복하기 위한 대안으로 개발되었다.

2013년 8월 6일 삼성전자가 세계 최초로 3차원 V낸드 양산에 성공하였다고 밝혔으며, 삼성전자에 따르면 3차원 V낸드는 기존 제품보다 40%가량 전력소비량이 적은 반면, 데이터 처리속도는 2배 이상 빠르며, 동일한 원재료(웨이퍼)로 만들 수 있는 양도 2배이다. 셀 수명을 판가름하는 쓰기 횟수도 2~10배 높일 수 있다.

'전자공학' 카테고리의 다른 글

| [반도체 공학] 도핑 방법과 PN 접합 (확산법, 이온주입법) (0) | 2021.05.06 |

|---|---|

| Bipolar Junction Transistor 의 구조와 동작원리 (0) | 2021.05.02 |

| [반도체 공정] 포토 공정(photolithography)에 대하여 (0) | 2021.05.01 |

| 이차전지의 원리와 소재 (양극 및 음극) (0) | 2021.05.01 |

| 반도체 웨이퍼의 부위별 명칭과 제조 공정 (0) | 2021.04.23 |

댓글